Hãy để ’ tiếp tục tìm hiểu quy trình tạo các phần lồi.

1. Tấm wafer đến và sạch:

Trước khi bắt đầu quy trình, bề mặt wafer có thể có các chất ô nhiễm hữu cơ, hạt, lớp oxit, v.v., cần được làm sạch bằng phương pháp giặt ướt hoặc khô.

2. PI-1 Litho: ( Quang khắc lớp thứ nhất: Quang khắc lớp phủ Polyimide)

Polyimide (PI) là vật liệu cách điện có tác dụng cách nhiệt và hỗ trợ. Đầu tiên nó được phủ lên bề mặt wafer, sau đó lộ ra, phát triển và cuối cùng tạo ra vị trí mở cho vết lồi.

3. Phún xạ Ti/Cu (UBM):

UBM là viết tắt của Under Bump Metallization, chủ yếu dành cho mục đích dẫn điện và chuẩn bị cho quá trình mạ điện tiếp theo. UBM thường được chế tạo bằng phương pháp phún xạ magnetron, với lớp mầm Ti/Cu là phổ biến nhất.

4. PR-1 Litho (Photolithography lớp thứ hai: Quang khắc quang học):

Quá trình quang khắc của chất quang dẫn sẽ xác định hình dạng và kích thước của các vết lồi, và bước này sẽ mở ra khu vực được mạ điện.

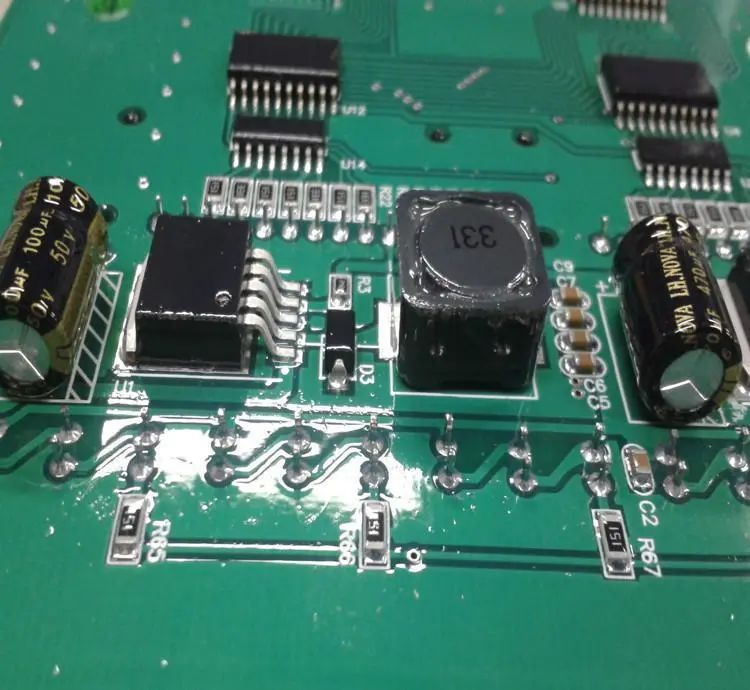

5. Mạ Sn-Ag:

Sử dụng công nghệ mạ điện, hợp kim thiếc-bạc (Sn-Ag) được lắng đọng tại vị trí mở để tạo thành các vết lồi lõm. Tại thời điểm này, các vết lồi không có hình cầu và chưa trải qua quá trình phản xạ nhiệt, như trong ảnh bìa.

6. Dải PR:

Sau khi mạ điện xong, chất quang dẫn (PR) còn lại sẽ được loại bỏ, để lộ lớp hạt kim loại đã phủ trước đó.

7. Khắc UBM:

Loại bỏ lớp kim loại UBM (Ti/Cu) ngoại trừ khu vực va đập, chỉ để lại lớp kim loại bên dưới các va đập.

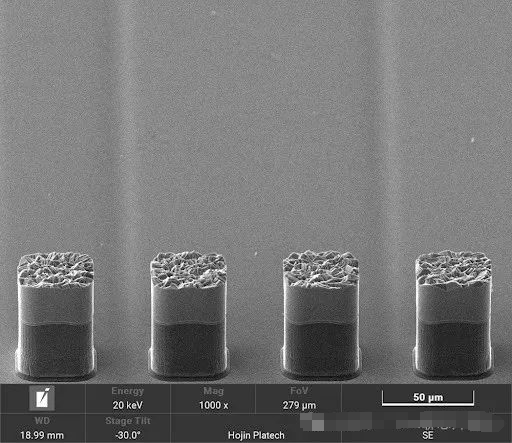

8. Chỉnh lại dòng:

Đi qua quá trình hàn nóng chảy lại để làm tan chảy lớp hợp kim thiếc-bạc và cho phép nó chảy trở lại, tạo thành hình dạng quả cầu hàn mịn.

9. Vị trí chip:

Sau khi quá trình hàn nóng chảy lại hoàn tất và các vết lồi lõm được hình thành, việc đặt chip được thực hiện.

Với điều này, quá trình lật chip đã hoàn tất.

Trong phần mới tiếp theo, chúng ta sẽ tìm hiểu quy trình về vị trí đặt chip.

Tiếng Việt

Tiếng Việt English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk اردو

اردو čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی தமிழ்

தமிழ் తెలుగు

తెలుగు नेपाली

नेपाली Burmese

Burmese български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski मराठी

मराठी Српски

Српски 简体中文

简体中文 Esperanto

Esperanto Afrikaans

Afrikaans Català

Català עִברִית

עִברִית Cymraeg

Cymraeg Galego

Galego 繁体中文

繁体中文 Latvietis

Latvietis icelandic

icelandic יידיש

יידיש Беларус

Беларус Hrvatski

Hrvatski Kreyòl ayisyen

Kreyòl ayisyen Shqiptar

Shqiptar Malti

Malti lugha ya Kiswahili

lugha ya Kiswahili አማርኛ

አማርኛ Bosanski

Bosanski Frysk

Frysk ជនជាតិខ្មែរ

ជនជាតិខ្មែរ ქართული

ქართული ગુજરાતી

ગુજરાતી Hausa

Hausa Кыргыз тили

Кыргыз тили ಕನ್ನಡ

ಕನ್ನಡ Corsa

Corsa Kurdî

Kurdî മലയാളം

മലയാളം Maori

Maori Монгол хэл

Монгол хэл Hmong

Hmong IsiXhosa

IsiXhosa Zulu

Zulu Punjabi

Punjabi پښتو

پښتو Chichewa

Chichewa Samoa

Samoa Sesotho

Sesotho සිංහල

සිංහල Gàidhlig

Gàidhlig Cebuano

Cebuano Somali

Somali Точик

Точик O'zbek

O'zbek Hawaiian

Hawaiian سنڌي

سنڌي Shinra

Shinra հայերեն

հայերեն Igbo

Igbo Sundanese

Sundanese Lëtzebuergesch

Lëtzebuergesch Malagasy

Malagasy Yoruba

Yoruba